Paper:

TSV Manufacturing Fault Modeling and Diagnosis Based on Multi-Tone Dither

Yuling Shang*, Min Tan*, Chunquan Li**,***,†, and Liyuan Sun*

*School of Electronic Engineering and Automation, Guilin University of Electronic Technology

1 Jinji Road, Guilin, Guangxi 541004, China

**School of Mechanical and Electrical Engineering, Guilin University of Electronic Technology

1 Jinji Road, Guilin, Guangxi 541004, China

***Guangxi Key Laboratory of Manufacturing System & Advanced Manufacturing Technology

Guilin 541004, China

†Corresponding author

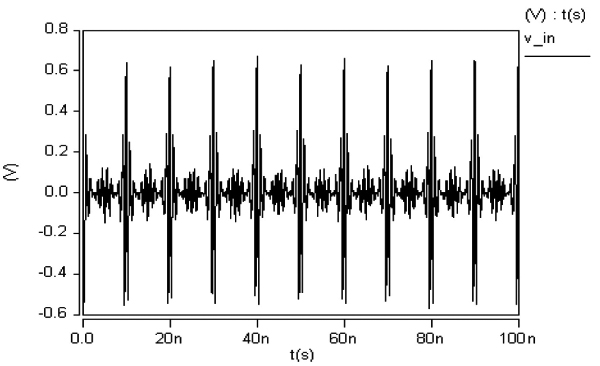

The faults in through-silicon via (TSV) have a critical impact on the reliability and yield of a three-dimensional integrated circuit (3-D IC). With the significant increase in the number of TSVs used in 3-D IC, the testing of TSVs for manufacturing faults poses certain serious challenges especially weak fault testing, and therefore it is important to have effective Design-For-Test (DFT) techniques. In this paper, we present a method for TSV testing using multi-tone dither signal, based on electrical characteristic analysis. This method mainly observes the differences in the root mean square (RMS) value of the output signal voltage between faultless and faulty TSV circuits to detect manufacturing faults, and uses only passive components such as metal lines, without consuming additional power for the testing. With regard to the common manufacturing faults such as voids and pinholes, the electrical characteristics of faulty TSVs are modeled and analyzed, and analytic equations of the faults, which are based on characteristic parameters, are explored. The ground-signal-TSV (GS-TSV) equivalent electrical model with manufacturing faults is simulated and tested by using a multi-tone dither test signal, which is generated by modulating an RF signal with an optimized multi-tone signal. The peak-to-average ratio (PAR) is used as the test evaluation parameter to determine the type and size of the fault. The simulation results demonstrate the effectiveness of the multi-tone dither test method in the detection of voids (as low as ohm level) and pinholes (up to mega ohm level). It is obvious that this method performs better in the diagnosis of weak manufacturing faults in TSVs.

The multi-tone dither complex test excitation used to diagnose TSV manufacturing faults"," providing as much information as possible about the presence"," the location and the geometrical characteristics of faults

- [1] Z. Zhu and Y. Yang, “Through-Silicon Via and three-dimensional integrated circuits,” Science Press, 2016.

- [2] D. H. Jung et al., “Through Silicon Via (TSV) Defect Modeling, Measurement, and Analysis,” IEEE Trans. on Components Packaging & Manufacturing Technology, Vol.7, Issue 1, pp. 138-152, 2017.

- [3] C. Li, M. Zou, Y. Shang, and M. Zhang, “Study on the Thermal Transient Response of TSV Considering the Effect of Electronic-Thermal Coupling,” J. of Semiconductor Technology & Science, Vol.15, No.3, pp. 356-364, 2015.

- [4] C. Okoro, J. W. Lau, F. Golshany, K. Hummler, and Y. S. Obeng, “A Detailed Failure Analysis Examination of the Effect of Thermal Cycling on Cu TSV Reliability,” IEEE Trans. on Electron Devices, Vol.61, No.1, pp. 15-22, 2014.

- [5] J. Marro, C. Okoro, Y. Obeng, and K. Richardson, “Defect and microstructural evolution in thermally cycled Cu through-silicon vias,” Microelectronics Reliability, Vol.54, No.11, pp. 2586-2593, 2014.

- [6] Y. Shang, Y. Zhao, C. Li, and P. Yang, “Study on the Crosstalk Characteristic of Non-ideal Interconnect Structure,” Int. J. of Materials & Structural Integrity, Vol.7, No.1, pp. 144-159, 2013.

- [7] S. Yu, L. Li, and J. Shao, “Three-dimensional integrated circuit test method,” Modern Computer, No.11, pp. 32-35, 2015.

- [8] P. Chen, L. Su, L. Du, G. Liao, and T. Shi, “Defect Inspection Technologies for TSV Based 3D Integration,” Semiconductor Technology, No.1, pp. 63-69, 2016.

- [9] Y. Lou, Z. Yan, F. Zhang, and P. D. Franzon, “Comparing Through-Silicon-Via (TSV) Void/Pinhole Defect Self-Test Methods,” J. of Electronic Testing, Vol.28, No.1, pp. 27-38, 2012.

- [10] J. Bian et al., “Pre-bonding TSV testing based on improved CAF-WAS,” Computer Engineering & Science, Vol.39, No.3, pp. 430-435, 2017.

- [11] S. Deutsch and K. Chakrabarty, “Contactless Pre-Bond TSV Test and Diagnosis Using Ring Oscillators and Multiple Voltage Levels,” IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, Vol.33, No.5, pp. 774-785, 2014.

- [12] Y. Shang, H. Yu, C. Li, and M. Tan, “Non-Contact Test method for TSV Fault based on Ring oscillator,” Semiconductor Technology, Vol.42, No.11, pp. 870-875, 2017.

- [13] L. Yu et al., “A 3D IC Self-test and Recovery Method Based on Through Silicon Via Defect Modeling,” J. of Electronics & Information Technology, Vol.34, No.9, pp. 2247-2253, 2012.

- [14] I. I. Basith, R. Rashidzadeh, and E. Abdel-Raheem, “Contactless detection of faulty TSV in 3D IC via capacitive coupling,” IEEE Int. Midwest Symp. on Circuits and Systems, pp. 1-4, 2015.

- [15] Y. Shang, B. Yin, and M. Tan, “Modeling and Analysis of TSV Crack Fault Based on Contactless Probe,” Semiconductor Technology, Vol.43, No.3, pp. 223-238, 2018.

- [16] D. Arumí, R. Rodríguez-Montañés, and J. Figueras, “Prebond Testing of Weak Defects in TSVs,” IEEE Trans. on Very Large Scale Integration Systems, Vol.24, No.4, pp. 1503-1514, 2016.

- [17] S. Kannan et al., “Embedded RF Circuit Diagnostic Technique with Multi-Tone Dither Scheme,” J. of Electronic Testing Theory & Applications, Vol.27, No.3, pp. 241-252, 2011.

- [18] Y. Shang and L. Sun, “Test for defect fault of TSV interconnect structure,” J. of Guilin University of Electronic Technology, Vol.37, No.5, pp. 382-386, 2017.

- [19] J. Kim, D. Jung, J. Cho, and J. S. Pak, “High-frequency measurements of TSV failures,” IEEE Electronic Components and Technology Conf., pp. 298-303, 2012.

- [20] R. Rodríguez-Montañés, D. Arumí, and J. Figueras, “Post-bond test of Through-Silicon Vias with open defects,” Test Symp., pp. 1-6, 2014.

- [21] Y. Shang, L. Sun, C. Li, and J. Ma, “Test of Mechanical Failure for Via Holes and Solder Joints of Complex Interconnect Structure,” J. of Electronic Testing Theory & Applications, Vol.33, No.4, pp. 491-499, 2017.

- [22] Q. Lu, Z. Zhu, Y. Liu, X. Liu, and X. Yin, “Wideband Electromagnetic Modeling of Coaxial-Annular Through-Silicon Vias,” IEEE Trans. on Electromagnetic Compatibility, Vol.60, Issue 6, pp. 1915-1922, 2017.

- [23] D. Han, S. Bhattacharya, and A. Chatterjee, “Low-cost parametric test and diagnosis of RF systems using multi-tone response envelope detection,” IET Computers & Digital Techniques, Vol.1, No.3, pp. 170-179, 2007.

- [24] G. Srinivasan et al., “Accurate Measurement of Multi-Tone Power Ratio (MTPR) of ADSL Devices Using Low Cost Testers,” IEEE European Symp. on Test, pp. 68-73, 2005.

- [25] B. Zhou, M. Jaksic, Z. Shen, and B. Wen, “Small-signal impedance identification of three-phase diode rectifier with multi-tone injection,” IEEE Applied Power Electronics Conf. and Exposition, pp. 2746-2753, 2014.

- [26] M. S. Saleh, M. H. El-Mahlawy, and A. B. Hassan, “Digital signature based test of analogue circuits using amplitude modulated multi-tone signals,” Int. Conf. on Microelectronics, 2017.

- [27] N. L’Esperance, T. Platt, M. Slamani, and T. Xia, “OFDM Multitone Signal Generation Technique for Analog Circuitry Test Characterization,” IEEE Trans. on Circuits & Systems II Express Briefs, Vol.63, No.6, pp. 583-587, 2016.

- [28] A. Bernieri, G. Betta, L. Ferrigno, and M. Laracca, “Crack Depth Estimation by Using a Multi-Frequency ECT Method,” IEEE Trans. on Instrumentation & Measurement, Vol.62, No.3, pp. 544-552, 2013.

- [29] A. Halder, S. Bhattacharya, and A. Chatterjee, “Automatic Multitone Alternate Test Generation For RF Circuits Using Behavioral Models,” Proc., ITC 2003, pp. 665-673, 2003.

This article is published under a Creative Commons Attribution-NoDerivatives 4.0 Internationa License.

This article is published under a Creative Commons Attribution-NoDerivatives 4.0 Internationa License.